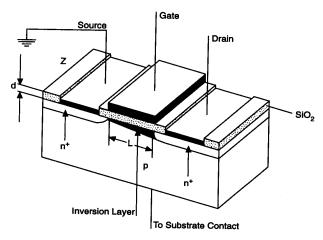

Figure 8.27 Schematics of a MOSFET with the p-type base n\*-doped for source and drain. A contact is attached directly to the substrate for threshold voltage adjustment. (After K.W. Böer, Survey of Semiconductor Physics, Vol. 2, Van Nostrand Reinhold, New York, 1992. With permission.)

$$I_{D} = \left(\frac{Z}{L}\right) \mu_{n} C_{o} \left\{ \left(V_{g} - 2V_{T} - \frac{V_{DS}}{2}\right) V_{DS} - \frac{2}{3C_{o}} \left(2\epsilon\epsilon_{o} e N_{A}\right)^{1/2} \left[\left(V_{DS} + 2V_{T}\right)^{3/2} - \left(2V_{T}\right)^{3/2}\right] \right\}$$

(8.37)

where  $C_{o}$  is the gate  $SiO_{2}$  layer's capacitance per unit area and

$$V_{T} = \frac{k_{B}T}{e} \ln \left( \frac{N_{A}}{n_{i}} \right).$$

For Z and L, see Figure 8.27.